USB engine emulator

Ruslana Fogler

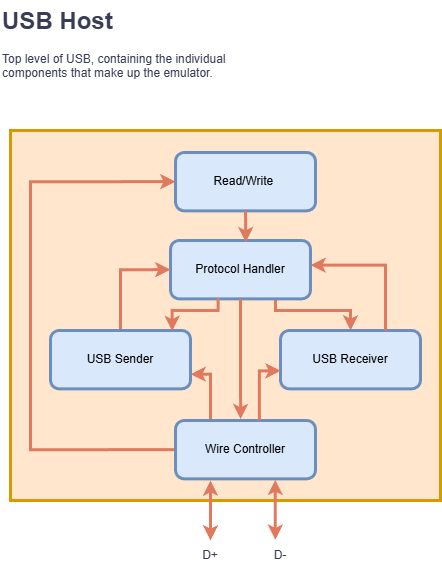

Description

For the final project in Logic Verification & Design at CMU, I solo'd the USB engine emulator partner project. This three week project involves implementing part of the USB 2.0 standard in SystemVerilog, and it focused on building coordinated hardware state machines that operated at multiple protocol layers. To abide by CMU's academic integrity policy, I do not have the code implementation for this project available.

Packet types implemented:

- Token packets: OUT, IN

- DATA packets: DATA0 (16 bit or 64 bit)

- Handshake packets: ACK, NACK

Protocol features implemented:

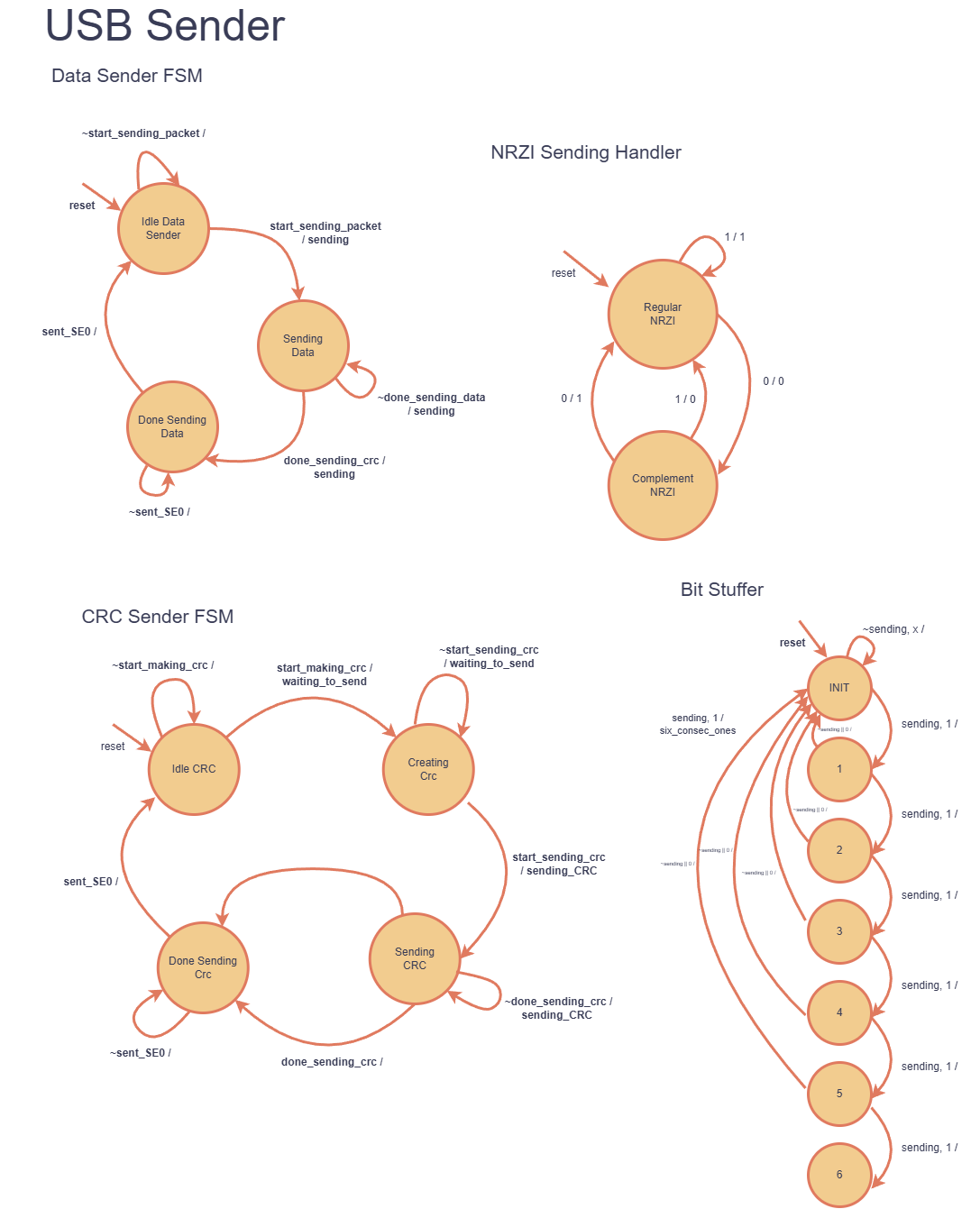

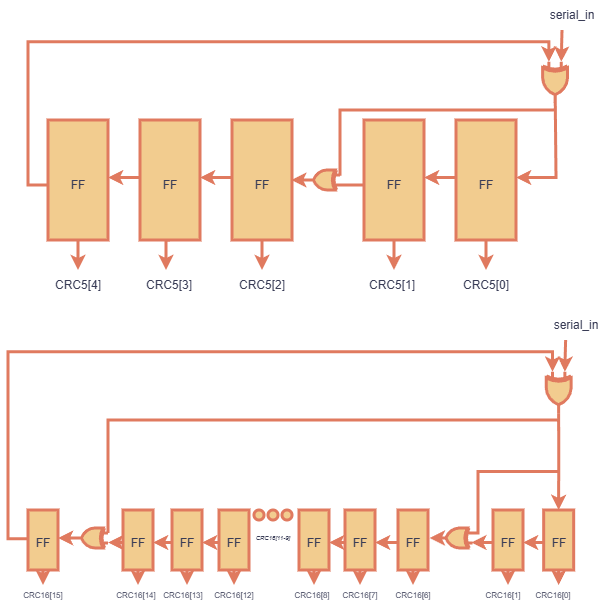

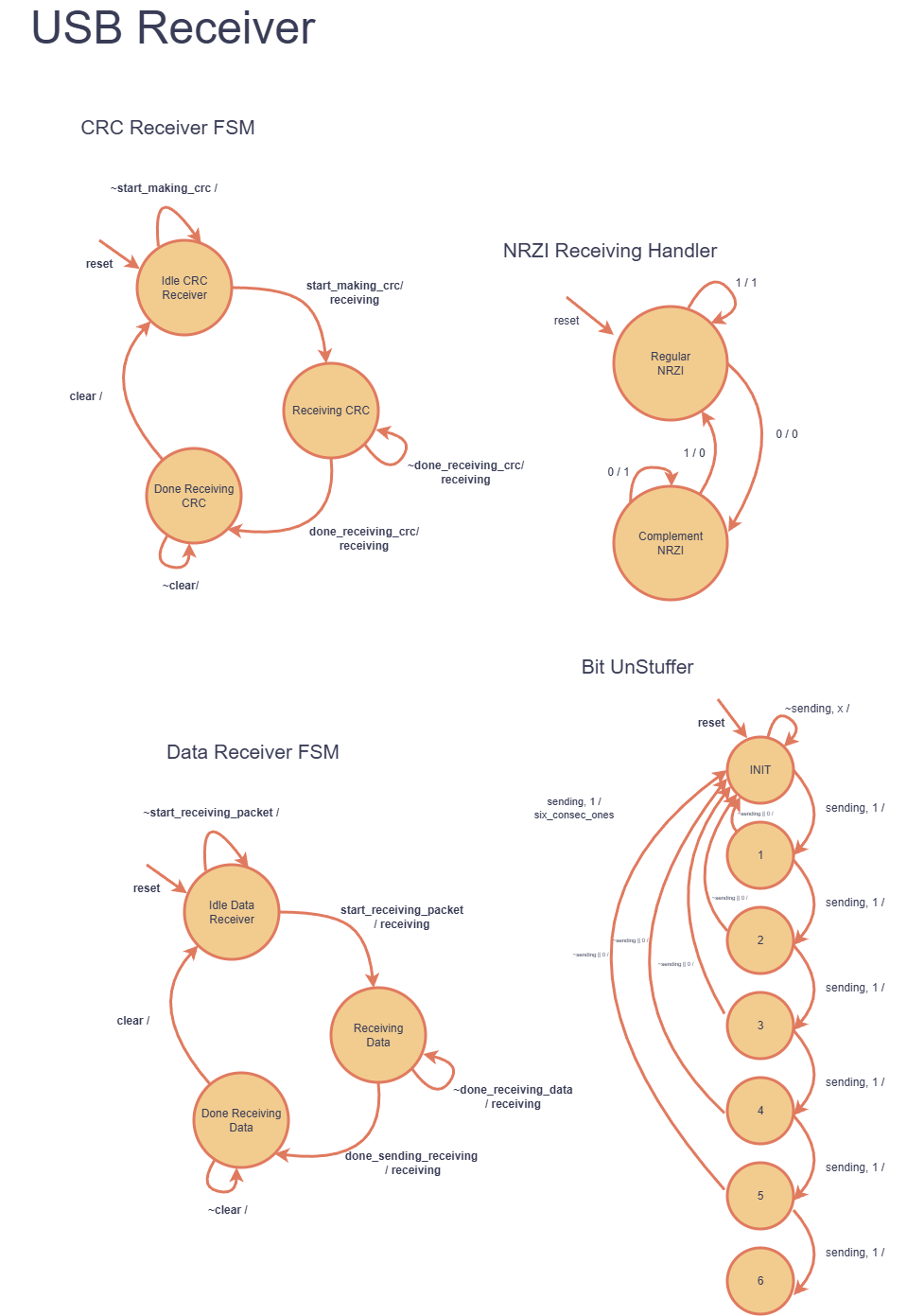

- Low-level encoding:

- NRZI encoding

- bit stuffing (after 6 consecutive 1s)

- CRC5/CRC16 generation and checking

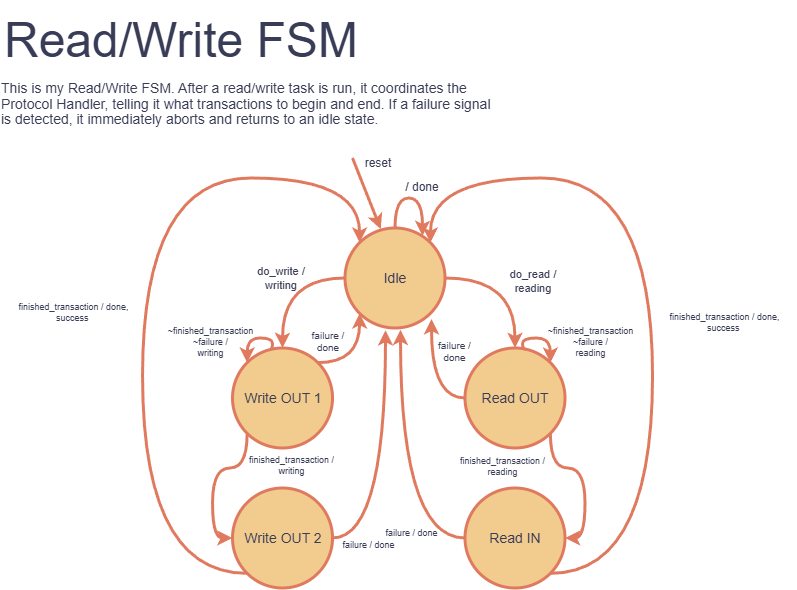

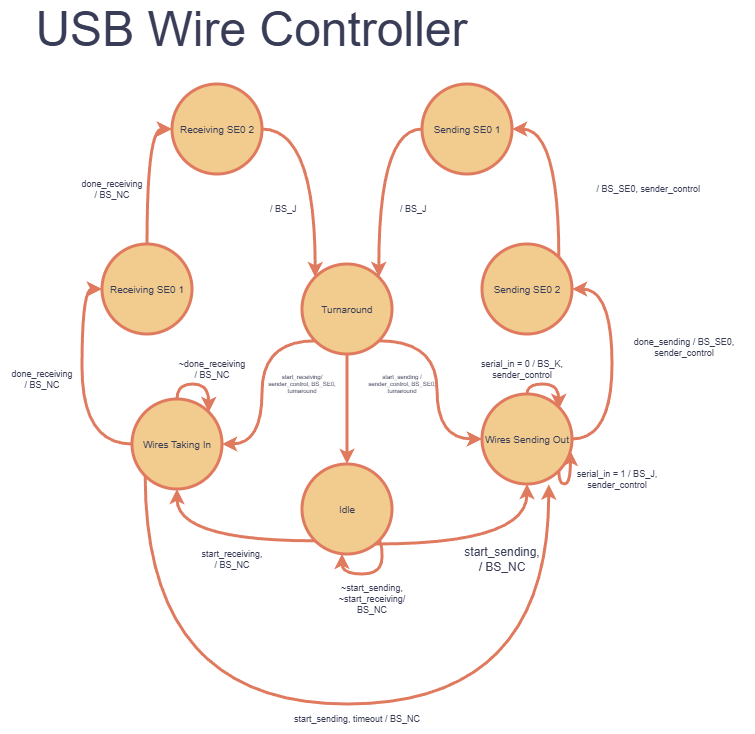

- Transaction-level error detection

- Automatic retry on corruption (up to 7 attempts)

- Timeout management (over 255 cycles)

- ACK/NACK handshaking

- READ: OUT transaction (send address) -> IN transaction (receive data)

- WRITE: OUT transaction (send address) -> OUT transaction (send data)

State machine diagrams: