RISClownin: custom RISC-V CPU

Ruslana Fogler, Bharathi Sridhar and Ankita Chatterjee

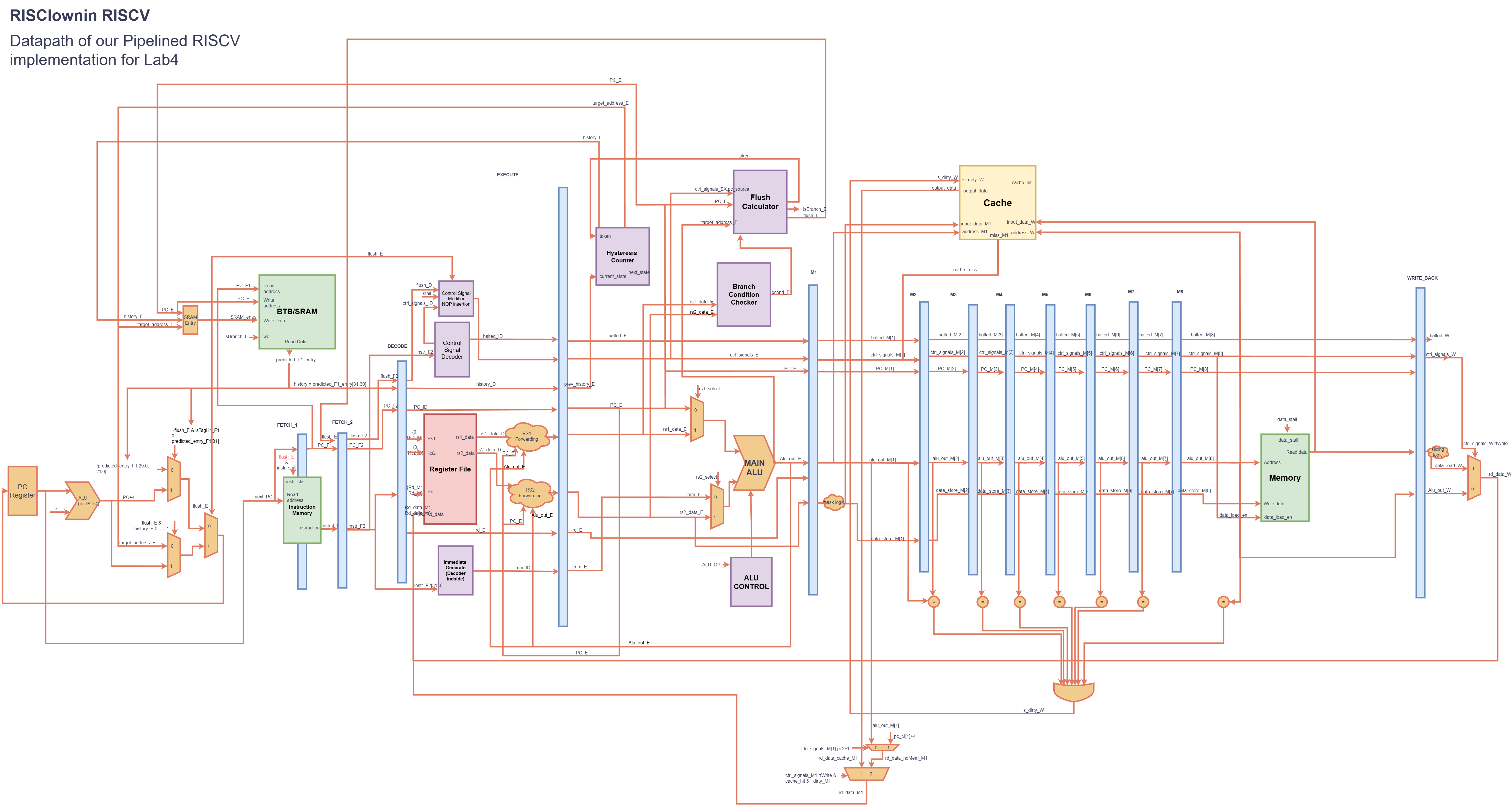

Description

Over the course of Intro to Computer Architecture (18447) at CMU, I worked alongside Ankita Chatterjee and Bharathi Sridhar to create a custom RISC-V CPU implementation in SystemVerilog. Over the course of five assignments, we handwrote the initial five stage pipeline (fetch, decode, execute, memory, writeback) and gradually added more features. Our CPU is supports 32 bit integer RISC-V instructions, including all arithmetic, control flow, load/store instructions in immediate/register formats. The design was tested with gcc-generated code.

Features include:

- Pipelining and stalls

- Data forwarding

- RAW hazard detection

- Hysteresis branch prediction, with a branch target buffer (BTB)

- Return address stack (RAS)

- Parameterizable set-associative cache